Dsmbga的热力仿真与耦合大尺寸hdfo的热力机械仿真

随着器件数量增加、功率密度提高和芯片异构集成(嗨)变得越来越普遍,电子封装也持续变得更加复杂。在移动领域,曾是印刷电路板(PCB)上独立元件的系统现已连同所有相关的被动器件和互连,成为单个系统级封装(SiP)类型组件的组成部分。大功率计算和数据中心封装也呈现类似趋势,其中内存已移至单个基于内插板的集成封装中。与现代先进封装的快速发展和复杂性增加相比,支配机械应力和热传递的物理定律保持不变。尽管近年来封装材料的发展取得了长足的进步,但还没有一种革命性的材料可以消除机械应力和热力问题。

为了在封装设计期间指导工程决策,机械(结构和热力)仿真是预测器件性能、研究器件故障、探索根本原因并执行优化研究的合适工具。这篇博客文章将重点介绍需要高仿真保真度的复杂封装所面临的独特挑战,并探讨使用仿真来分析封装热性能的两项案例研究。

案例研究 1:移动市场封装

第一项案例研究描述了系统级封装器件用于移动市场的场景。该封装预计将夹放在两个堆叠的印刷电路板(PCB)之间,这限制了给封装散热的可用选项:热量必须传导到PCB,而有限的总封装厚度使其无法安装顶部铜散热器。

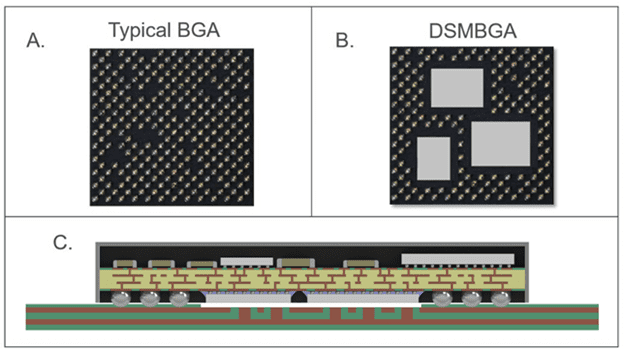

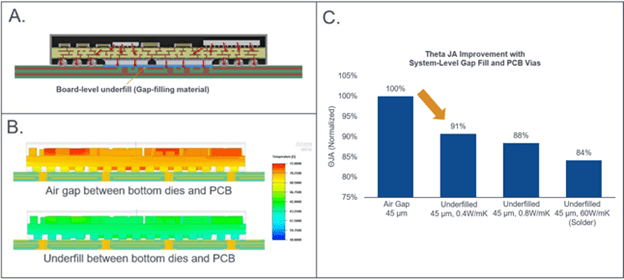

已针对双面模塑球栅阵列(DSMBGA)的以下改良进行了测试:高导热率环氧树脂模塑化合物(EMC);使用大型铜(铜)柱取代BGA;用来密封底部外露式晶片和PCB之间间隙的系统级底部填充(见图1)。在这些选项中,只有系统级底部填充提供了明显的热力提升:在标准的电平无风环境下,接面到环境热阻(ΘJA)减少了约10%。铜柱提升可以忽略不计、高导热率emc带来的提升不足1%(见图2)。该仿真结果借由Siemens Simcenter Flotherm辅助完成。

图1:典型BGA器件(A)和DSMBGA器件(B)之间的BGA布局差异,有源元件和芯片位于基板底部。(C)显示DSBGA器件的代表性横截面

图2:(A)基板底部填充位于基板底部晶片下方的位置。(B)非底部填充(顶)和底部填充(底)封装之间的仿真温差。图像之间的色标一致。(C)不同底部填充导热率的仿真结果图

案例研究 2:大尺寸封装

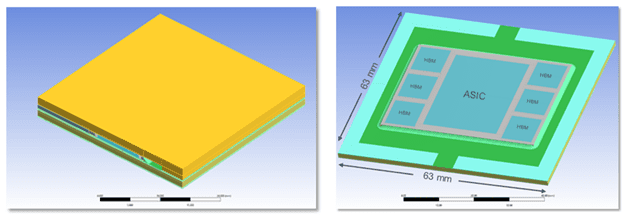

本演示文稿中的第二项案例研究是对带有中央专用集成电路(asic)和多个高带宽存储器(hbm)模块的大尺寸高密度扇出型(HDFO)封装进行耦合结构热力仿真(见图3)。大多数热力仿真呈现的结果是(出于速度和简易性考虑),在ASIC / HBM模块顶部和盖板底部之间的热界面材料(TIM)焊接线厚度恒定。在这项研究中,希望更好地了解跨ASIC和模块区域的焊接线厚度变化(由于翘曲)如何影响封装的热性能。

图3:大尺寸HDFO模型。四分对称视图(左)。展开视图(右),盖板已隐藏以显示ASIC + 6 HBM HDFO模块

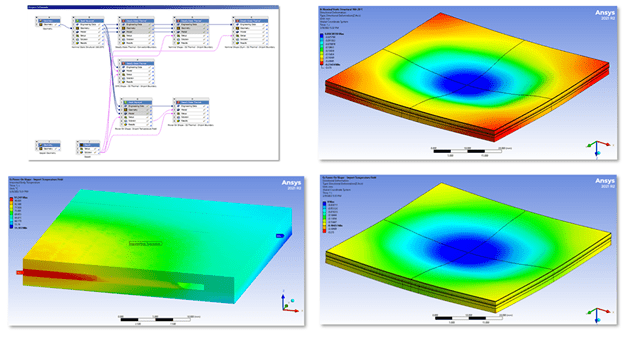

首先在Ansys Icepak中模拟63 x 63毫米HDFO封装,以生成可应用于Ansys Workbench机械中结构的“上电”温度曲线。该温度曲线有两个目的:其一,作为温度条件应用于整个结构模型以产生应力,并计算由于每种材料的不同热膨胀系数而导致的模型变形,其二,计算盖板顶部和基板底部的温度边界条件,以应用于包含结构变形和蒂姆焊接线变化的Ansys机械稳态热力仿真(见图4)。

图4:(顺时针,从左上角开始)显示耦合热模型和结构模型的关联子系统的Ansys项目原理图;封装翘曲,20°C,死区视图(查看基板底部);已应用“上电”热梯度的封装翘曲死区视图(与20°C翘曲相同的色标);从Icepak导入时的温度曲线边界条件

图4:(顺时针,从左上角开始)显示耦合热模型和结构模型的关联子系统的Ansys项目原理图;封装翘曲,20°C,死区视图(查看基板底部);已应用“上电”热梯度的封装翘曲死区视图(与20°C翘曲相同的色标);从Icepak导入时的温度曲线边界条件

然后将变形的结构(在20°C室温翘曲基线和Icepak仿真的“上电”温度下计算)用作热模型的结构。有源表面接面温度的变化(相对于未变形基线的测量)已计算并报告整个晶片表面的情况(见图5)。

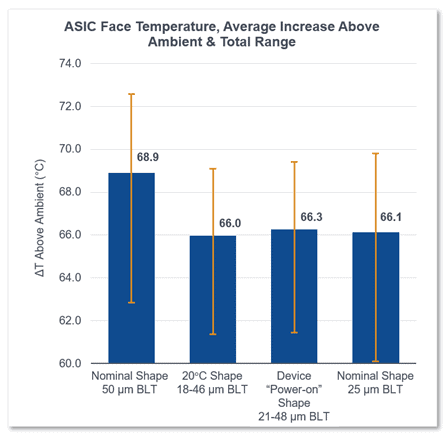

图5:不同仿真asic温度的温度结果图表。误差条代表整个晶面上的总温度范围

结论

Ansys机械热模型报告晶面的平均ASIC温度为88.9°C,最高温度为92.6°C,最低温度为82.8°C(整块晶片温差为9.7°C)。20°C形状模型报告的晶片温度平均为86.0°C,最高为89.1°C,最低为81.4°C(整块晶片温差为7.7°C)。“上电”形状模型报告的晶片温度平均为86.3°C,最高为89.4°C,最低为81.4°C(整块晶片温差为8.0°C)。

由于模块中心的焊接线较薄而模块角部的焊接线较厚(相对于50µm BLT基线),考虑到焊接线厚度(BLT)变化,模型中晶片温度似乎更加一致(整块晶片的温差较小)。本案例研究可以帮助人们更好地了解未来模型的不确定性。

关于作者

Nathan Whitchurch是Amkor支持封装和机械仿真的高级工程师。进入电子封装领域之前,惠特从事的项目包括车载计算机机架外壳,无线电热设计,数据中心热分析和系统集成。他从封装级的层次出发,提供了系统级背景知识以及对机械仿真的理解。惠特彻奇拥有南加州大学机械工程学士学位。